الإصدار الاحترافي من برنامج Intel High-Level Synthesis Compiler Pro

معلومات المنتج

| اسم المنتج | الإصدار الاحترافي من برنامج Intel High-Level Synthesis Compiler Pro |

|---|---|

| إصدار | 22.4 |

| تاريخ الافراج عنه | 19 ديسمبر 2022 |

| إشعار الإهمال | ومن المقرر أن يكون المترجم التجميعي Intel High-Level تم إهماله بعد الإصدار 23.4. |

تعليمات استخدام المنتج

دليل البدء

- تهيئة بيئة المترجم الخاص بك.

- Review تصميم مختلف السابقينampالملفات والبرامج التعليمية المقدمة مع مترجم Intel HLS.

دليل المستخدم

- يوفر دليل المستخدم تعليمات حول

- تجميع والتحقق من ومحاكاة الملكية الفكرية (IP) المصممة لمنتجات Intel FPGA.

- متابعة تدفق التطوير الكامل للمكون الخاص بك بدءًا من إنشاء المكون الخاص بك واختباره وحتى دمج IP المكون الخاص بك في نظام أكبر باستخدام برنامج Intel Quartus Prime.

دليل أفضل الممارسات

يوفر دليل أفضل الممارسات التقنيات والممارسات التي يمكنك تطبيقها لتحسين استخدام منطقة FPGA وأداء مكون HLS الخاص بك. قم بتطبيق أفضل الممارسات هذه بعد التحقق من الصحة الوظيفية للمكون الخاص بك.

دليل مرجعي

يوفر الدليل المرجعي معلومات مرجعية حول الميزات التي يدعمها برنامج التحويل البرمجي Intel HLS. ابحث عن تفاصيل حول خيارات أمر Intel HLS Compiler، الرأس files، والبراغمات، والسمات، ووحدات الماكرو، والإعلانات، والوسائط، ومكتبات القوالب.

Intel® High Level Synthesis Compiler Pro Edition الإصدار 22.4 ملاحظات الإصدار

- توفر ملاحظات الإصدار Intel® High Level Synthesis Compiler Pro Edition معلومات حديثة حول الإصدار 22.4 من Intel High Level Synthesis Compiler Pro Edition.

في انتظار الإهمال لمترجم Intel HLS

- للاحتفاظ بإمكانية الوصول إلى أحدث ميزات التصميم عالية المستوى FPGA والتحسينات وأدوات التطوير المساعدة، قم بترحيل تصميماتك الحالية لاستخدام مجموعة أدوات Intel oneAPI Base Toolkit.

- من المقرر أن يتم إهمال مترجم Intel High Level Synthesis (HLS) بعد الإصدار 23.4.

- تفضل بزيارة صفحة منتج Intel oneAPI للحصول على نصائح بشأن الترحيل، أو انتقل إلى منتدى مجتمع Intel High Level Design لطرح أي أسئلة أو طلبات.

حول مكتبة وثائق Intel HLS Compiler Pro Edition

- يتم تقسيم الوثائق الخاصة بإصدار Intel HLS Compiler Pro عبر عدد قليل من المنشورات. استخدم الجدول التالي للعثور على المنشور الذي يحتوي على معلومات Intel HLS Compiler Pro Edition التي تبحث عنها:

الجدول 1. مكتبة وثائق Intel High-Level Synthesis Compiler Pro Edition

| العنوان والوصف | |

| ملاحظات الإصدار

يوفر أحدث المعلومات حول مترجم Intel HLS. |

وصلة |

| دليل البدء

ابدأ العمل باستخدام برنامج Intel HLS Compiler من خلال تعلم كيفية تهيئة بيئة برنامج التحويل البرمجي لديك وإعادة تشغيلهviewجي التصميم المختلفة على سبيل المثالampالملفات والبرامج التعليمية المقدمة مع مترجم Intel HLS. |

وصلة |

| دليل المستخدم

يوفر إرشادات حول تركيب الملكية الفكرية (IP) والتحقق منها ومحاكاتها التي تصممها لمنتجات Intel FPGA. قم بمراجعة تدفق التطوير الكامل للمكون الخاص بك بدءًا من إنشاء المكون الخاص بك واختباره حتى دمج IP المكون الخاص بك في نظام أكبر باستخدام برنامج Intel Quartus Prime. |

وصلة |

| دليل أفضل الممارسات

يوفر التقنيات والممارسات التي يمكنك تطبيقها لتحسين استخدام منطقة FPGA وأداء مكون HLS الخاص بك. عادةً ما تقوم بتطبيق أفضل الممارسات هذه بعد التحقق من الصحة الوظيفية للمكون الخاص بك. |

وصلة |

| دليل مرجعي

يوفر معلومات مرجعية حول الميزات التي يدعمها برنامج Intel HLS Compiler. ابحث عن تفاصيل حول خيارات أمر Intel HLS Compiler، الرأس files، والبراغمات، والسمات، ووحدات الماكرو، والإعلانات، والوسائط، ومكتبات القوالب. |

وصلة |

شركة إنتل. كل الحقوق محفوظة. تعد Intel وشعار Intel وعلامات Intel الأخرى علامات تجارية لشركة Intel Corporation أو الشركات التابعة لها. تضمن Intel أداء منتجات FPGA وأشباه الموصلات وفقًا للمواصفات الحالية وفقًا لضمان Intel القياسي ، ولكنها تحتفظ بالحق في إجراء تغييرات على أي منتجات وخدمات في أي وقت دون إشعار. لا تتحمل Intel أي مسؤولية أو التزام ناشئ عن التطبيق أو استخدام أي معلومات أو منتج أو خدمة موصوفة هنا باستثناء ما تم الاتفاق عليه صراحةً كتابةً من قبل Intel. يُنصح عملاء Intel بالحصول على أحدث إصدار من مواصفات الجهاز قبل الاعتماد على أي معلومات منشورة وقبل تقديم طلبات المنتجات أو الخدمات.

*قد يتم المطالبة بأسماء وعلامات تجارية أخرى باعتبارها ملكًا للآخرين.

في انتظار الإهمال لمترجم Intel HLS

- للاحتفاظ بإمكانية الوصول إلى أحدث ميزات التصميم عالية المستوى FPGA والتحسينات وأدوات التطوير المساعدة، قم بترحيل تصميماتك الحالية لاستخدام مجموعة أدوات Intel oneAPI Base Toolkit.

- من المقرر أن يتم إهمال مترجم Intel High Level Synthesis (HLS) بعد الإصدار 23.4.

- تفضل بزيارة صفحة منتج Intel oneAPI للحصول على نصائح بشأن الترحيل، أو انتقل إلى منتدى مجتمع Intel High Level Design لطرح أي أسئلة أو طلبات.

الميزات والتحسينات الجديدة

- يتضمن الإصدار 22.4 من Intel High Level Synthesis Compiler Pro الإصدار XNUMX الميزات الجديدة التالية:

- الافراج عن صيانة.

- لا توجد ميزات أو تحسينات جديدة للإصدار 22.4 من Intel HLS Compiler Pro.

التغييرات في سلوك البرمجيات

- يوثق هذا القسم الحالات التي تغيرت فيها ميزات Intel HLS Compiler Pro Edition الإصدار 22.4 من الإصدارات السابقة للمترجم.

الافراج عن صيانة.

- لا توجد تغييرات في سلوك البرنامج للإصدار 22.4 من Intel HLS Compiler Pro Edition.

المتطلبات الأساسية لـ Intel High-Level Synthesis Compiler Pro Edition

- يعد Intel HLS Compiler Pro Edition جزءًا من مجموعة التصميم Intel Quartus® Prime Pro Edition. يمكنك تثبيت برنامج Intel HLS Compiler كجزء من تثبيت برنامج Intel Quartus Prime أو تثبيته بشكل منفصل. يتطلب استخدام Intel Quartus Prime وبرامج إضافية.

- للحصول على إرشادات مفصلة حول تثبيت برنامج Intel Quartus Prime Pro Edition، بما في ذلك متطلبات النظام والمتطلبات الأساسية ومتطلبات الترخيص، راجع تثبيت برنامج Intel FPGA وترخيصه.

- يتطلب برنامج Intel HLS Compiler البرامج التالية بالإضافة إلى Intel Quartus Prime:

مترجم C++

- في Linux، يتطلب برنامج Intel HLS Compiler الإصدار 9.3.0 من مجلس التعاون الخليجي بما في ذلك مكتبة GNU C++ والأدوات المساعدة الثنائية (binutils).

- يتم توفير هذا الإصدار من دول مجلس التعاون الخليجي كجزء من تثبيت برنامج Intel HLS Compiler الخاص بك. بعد تثبيت برنامج التحويل البرمجي Intel HLS، يتوفر الإصدار 9.3.0 من إصدار مجلس التعاون الخليجي /مجلس التعاون الخليجي.

- مهم: يستخدم مترجم Intel HLS /gcc الدليل كدليل سلسلة الأدوات الخاص به. استخدم هذا التثبيت لـGC لجميع أعمال التصميم المتعلقة بـ HLS.

- بالنسبة لنظام التشغيل Windows، قم بتثبيت أحد الإصدارات التالية من Microsoft* Visual Studio* Professional:

- مايكروسوفت فيجوال ستوديو 2017 بروفيشنال

- مجتمع Microsoft Visual Studio 2017

- للحصول على أحدث دعم لـ C++ 17، تأكد من أنك تستخدم أحدث إصدار من Visual Studio 2017.

- مهم: لا يدعم برنامج Intel HLS Compiler إصدارات Microsoft Visual Studio غير تلك المحددة لإصدار البرنامج.

برنامج المحاكاة Siemens* EDA Questa®

- في أنظمة Windows وRedHat Linux، يمكنك تثبيت برنامج محاكاة Questa® من مثبت برنامج Intel Quartus Prime. الخيارات المتاحة هي كما يلي:

- كويستا إنتل FPGA الطبعة

- كويستا إنتل FPGA النسخة المبتدئة

- يتطلب كل من Questa Intel FPGA Edition وQuesta Intel FPGA Starter Edition تراخيص. ترخيص Questa Intel FPGA Starter Edition مجاني. للحصول على التفاصيل، راجع تثبيت برنامج Intel FPGA وترخيصه.

- وبدلاً من ذلك، يمكنك استخدام الإصدار المرخص الخاص بك من برنامج Siemens* EDA ModelSim* SE أو Siemens EDA Questa Advanced Simulator.

- في أنظمة Linux، يتطلب Questa – Intel FPGA Edition وQuesta – Intel FPGA Starter Edition حزم أدوات التطوير Red Hat*.

- للحصول على معلومات حول كافة إصدارات برنامجي ModelSim وQuesta التي يدعمها برنامج Intel، راجع قسم معلومات واجهة EDA في ملاحظات إصدار دعم البرامج والأجهزة لإصدارك من Intel Quartus Prime Pro Edition.

معلومات ذات صلة

- دليل البدء للمترجم التجميعي عالي المستوى من Intel

- أنظمة التشغيل المدعومة

- متطلبات البرامج في تثبيت برامج Intel FPGA وترخيصها

- معلومات واجهة EDA (إصدار Intel Quartus Prime Pro)

المشكلات المعروفة والحلول

- يوفر هذا القسم معلومات حول المشكلات المعروفة التي تؤثر على الإصدار 22.4 من Intel HLS Compiler Pro Edition.

| وصف | الحل البديل |

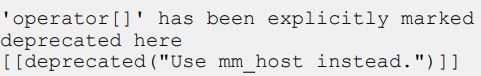

| عند استخدام الفئة المهملة mm_master، يرسل المترجم رسالة تحذير مثل ما يلي:

لا تشير هذه الرسالة إلى الجزء الذي يحتاج إلى تغيير في التعليمات البرمجية الخاصة بك. |

تجنب رسالة التحذير هذه باستخدام الفئة mm_host، التي تحل محل الفئة المهملة mm_master. |

| (في نظام التشغيل Windows فقط) يمكن أن يؤدي تجميع التصميم في دليل باسم مسار طويل إلى فشل الترجمة.

تحقق من debug.log file ل "لا يمكن العثور عليها file"أخطاء. يمكن أن تشير هذه الأخطاء إلى أن المسار الخاص بك طويل جدًا. |

قم بتجميع التصميم في دليل باسم مسار قصير. |

| (نظام التشغيل Windows فقط) يمكن أن يمنعك المسار الطويل لدليل تثبيت Intel Quartus Prime من تجميع وتشغيل البرامج التعليمية لمترجم Intel HLS والإصدارات السابقة بنجاح.ampلو تصاميم.

تحقق من debug.log file ل "لا يمكن العثور عليها file"أخطاء. يمكن أن تشير هذه الأخطاء إلى أن المسار الخاص بك طويل جدًا. |

نقل الدروس والسابقينamples إلى اسم مسار قصير قبل محاولة تشغيلها. |

| وصف | الحل البديل |

| لا يمكن للمكتبات التي تستهدف OpenCL* والمكتوبة بلغة HLS استخدام التدفقات أو الأنابيب كواجهة بين كود OpenCL والمكتبة المكتوبة بلغة HLS.

ومع ذلك، يمكن للمكتبة في HLS استخدام التدفقات أو الأنابيب إذا كانت كلا نقطتي النهاية داخل المكتبة (على سبيل المثالample، وهو دفق يربط بين وظيفتين مهمتين). |

غير متاح |

| يمكن أن يؤدي تطبيق معلمة ihc::maxburst على واجهات مضيف Avalon® Memory-Mapped إلى تعليق تصميمك في المحاكاة. | غير متاح |

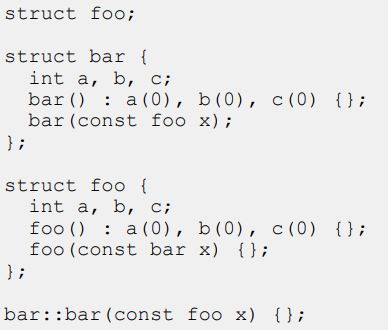

| في بعض الحالات غير الشائعة، إذا كان لديك فئتان يتطلب كل منشئيهما مثيلات للفئة الأخرى كمدخل، فقد يتعطل المترجم.

على سبيل المثالample، يؤدي تجميع مقتطف التعليمات البرمجية التالي إلى تعطل برنامج التحويل البرمجي:

|

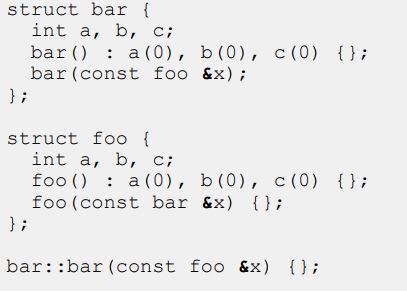

تجنب إنشاء تعريف دائري. بدلاً من ذلك، استخدم مؤشرًا أو مرجعًا في مُنشئ النسخ الخاص بك.

على سبيل المثالample، قم بتحويل مقتطف التعليمات البرمجية السابق إلى التعليمة البرمجية التالية وتمرير البنية كمرجع إلى المُنشئ:

|

| المكتبات التي تستهدف OpenCL والمكتوبة بلغة HLS قد تتسبب في حصول نواة OpenCL التي تتضمن المكتبة على تجميع تزايدي أكثر تحفظًا. | غير متاح |

| عند تطوير مكتبة، إذا كان لديك تعريف #define لقيمة ستستخدمها لاحقًا في #pragma، فسيفشل الأمر fpga_crossgen.

على سبيل المثالample، لا يمكن ترجمة التعليمات البرمجية التالية بواسطة

|

استخدم pragma بدلاً من #pragma.

على سبيل المثالample، يتم تجميع ما يلي بنجاح مع ملف

|

| عند استخدام خيار الأمر -c للحصول على تجميع وربط منفصلينtages في سير العمل الخاص بك، وإذا لم تحدد خيار -march في s الارتباطtage (أو حدد قيمة خيار -march مختلفة)، الارتباط الخاص بكtagقد تفشل مع أو بدون رسائل خطأ. | تأكد من أنك تستخدم نفس قيمة خيار -march لكلا التجميعين باستخدام خيار الأمر -ctage والربط stage. |

| وصف | الحل البديل |

| يؤدي تطبيق سمة الذاكرة hls_merge على مصفوفة تم الإعلان عنها داخل حلقة غير ملفوفة أو مفتوحة جزئيًا إلى دمج نسخ من المصفوفة عبر تكرارات الحلقة غير المسجلة.

|

تجنب استخدام سمة الذاكرة hls_merge في الحلقات غير المسجلة.

إذا كنت بحاجة إلى دمج الذكريات في حلقة غير ملفوفة، فقم بالإعلان بوضوح عن مصفوفة من نوع البنية لدمج العرض، أو قم بإعلان مصفوفة أعمق لدمج العمق.

|

| في الذاكرة الوظيفية Viewفي تقرير التصميم عالي المستوى، قد تظهر بعض الذكريات ذات النطاق الوظيفي على أنها "مُحسَّنة بعيدًا". | لا أحد.

عندما يكون file يحتوي على وظائف هي مكونات ووظائف ليست مكونات، ويتم إدراج كافة المتغيرات الخاصة بنطاق الوظيفة في جزء قائمة ذاكرة الوظائف، ولكن المتغيرات من المكونات فقط هي التي تحتوي على معلومات عنها لإظهارها في ذاكرة الوظائف View لوحة. |

| تفشل بعض تقارير التصميم عالية المستوى في Microsoft Internet Explorer*. | استخدم أحد المتصفحات التالية view تقارير:

• جوجل كروم* • مايكروسوفت إيدج* • موزيلا فايرفوكس* |

| الحلقة Viewيوجد في تقارير التصميم عالية المستوى القيود التالية:

• لم يتم تصميم سلوك المجموعات الخالية من المماطلة في الحلقة Viewإيه. الكمون النهائي الموضح في الحلقة Viewعادةً ما يكون زمن الاستجابة لمجموعة خالية من المماطلة أكثر تشاؤمًا (أي أعلى) من زمن الوصول الفعلي لتصميمك. للحصول على وصف للمجموعات والمجموعات الخالية من المماطلة، راجع تجميع مسار البيانات في إنتل رفيع المستوى دليل أفضل الممارسات لـ Synthesis Compiler Pro Edition. • لا يتم تصميم الأكشاك من عمليات القراءة والكتابة من الذاكرة أو بيانات الطباعة. • تؤدي أعداد التكرارات العالية (> 1000) إلى بطء أداء الحلقة Viewاه. • لا يمكنك تحديد عدد تكرار يساوي صفر (0) في الحلقة Viewاه. |

لا أحد. |

| الارتباطات الموجودة في بعض التقارير في تقارير التصميم عالية المستوى التي تم إنشاؤها على أنظمة Windows لا تعمل. | قم بإنشاء تقارير التصميم عالية المستوى (أي تجميع التعليمات البرمجية الخاصة بك) على نظام Linux. |

| استخدام بنية من نوع بيانات واحد ac_int في واجهة متدفقة تستخدم الحزم (ihc::usesPackets ) لا يعمل.

على سبيل المثالample، مقتطف التعليمات البرمجية التالي لا يعمل:

|

لاستخدام هذه المجموعة في التصميم الخاص بك، اتبع القيود التالية:

• يجب أن يكون حجم بيانات ac_int الداخلي مضاعفًا للرقم 8 • يجب تحديد إعلان نوع واجهة الدفق ihc::bitsPerSymbol<8> على سبيل المثالample، يعمل مقتطف الكود التالي:

|

| وصف | الحل البديل | |

| عند تشغيل محاكاة عالية الإنتاجية للمكون الخاص بك باستخدام استدعاءات دالة قائمة الانتظار، إذا لم تستخدم الدالة ihc_hls_component_run_all لتشغيل استدعاءات المكونات المدرجة في قائمة الانتظار بعد كافة استدعاءات ihc_hls_enqueue لهذا المكون، تحدث السلوكيات التالية:

• في المحاكاة، يتم تشغيل وظائف المكونات الموجودة في قائمة الانتظار. • في المحاكاة، لا يتم تشغيل وظائف المكونات الموجودة في قائمة الانتظار، مع عدم وجود رسائل خطأ أو تحذير. |

تأكد من أنك تستخدم الدالة ihc_hls_component_run_all بعد كافة استدعاءات ihc_hls_enqueue لهذا المكون لتشغيل استدعاءات دالة المكون الموضوعة في قائمة الانتظار. | |

| إطلاق وظيفة مهمة باستخدام ihc::launch_always_run | لتجنب تجريد التحسين، أضف فترة(1) | |

| يزيل سمات التحسين المطبقة على المهمة | حلقة إلى الوظيفة المتأثرة تطبق عنصر التحكم المقابل | |

| وظيفة. | pragma إلى حلقة while(1) بدلاً من الوظيفة. | |

| في الكود التالي السابقينample، يتم تجاهل السمة المطبقة على الوظيفة. تعرض تقارير التصميم عالية المستوى II من 1 لهذه المهمة بدلاً من II المطلوب من 4. | الكود التالي على سبيل المثالampأظهر كيف يمكنك تنفيذ هذا التغيير للكود السابق على سبيل المثالampعلى: | |

|

|

|

| بالنسبة لمشروعات Cyclone® V التي تحتوي على مكونات HLS متعددة، عند استخدام الأمر i++ لتجميع مشروعك إلى الأجهزة (i++ -march=CycloneV)، قد تتلقى خطأ.

بينما يختلف نص الخطأ وفقًا لمشروعك، فإن توقيع الخطأ هو فشل في تجميع Intel Quartus Prime بسبب بناء جملة Verilog غير صحيح. تحاول إحدى الوحدات استخدام وظيفة لا يستطيع مترجم Intel Quartus Prime العثور عليها. |

إذا واجهت هذه المشكلة، ضع كل مكون من مكونات HLS في مشروع منفصل. | |

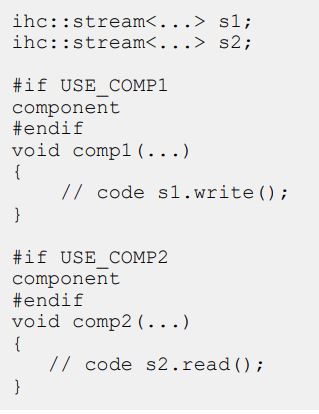

| يؤدي تجميع بعض التصميمات التي تحتوي على مكونات متعددة إلى حدوث خطأ حول إعادة استخدام التدفق. | إذا واجهت هذه المشكلة، قم بتجميع كل مكون في التصميم بشكل منفصل. قد تحتاج إلى إضافة وحدات ماكرو إلى التعليمات البرمجية الخاصة بك لتمكين تجميع كل مكون بشكل منفصل. | |

| ضع في اعتبارك السابق التاليampعلى: | ||

|

||

أرشيف ملاحظات إصدار برنامج Intel High-Level Synthesis Compiler Pro Edition

للحصول على أحدث الإصدارات والإصدارات السابقة من دليل المستخدم هذا، راجع ملاحظات إصدار Intel HLS Compiler Pro Edition. إذا لم يكن إصدار البرنامج مدرجًا، فسيتم تطبيق ملاحظات الإصدار الخاصة بإصدار البرنامج السابق.

محفوظات مراجعة المستندات لملاحظات الإصدار Intel HLS Compiler Pro Edition 22.4

| نسخة الوثيقة | إصدار Intel Quartus Prime | التغييرات |

| 2022.12.19 | 22.4 | • الإصدار الأولي. |

المستندات / الموارد

|

إنتل عالي المستوى التجميعي المترجم برو الطبعة [بي دي اف] تعليمات الإصدار 22.4، الإصدار 23.4، الإصدار الاحترافي من برنامج التحويل البرمجي عالي المستوى، الإصدار الاحترافي من برنامج التحويل البرمجي عالي المستوى |